3纳米?三星“下世代”芯片要碾压苹果高通!

自家的7nm制程的芯片还没见到影子,三星就急着用嘴“抢发”了3nm工艺。

近日,三星在其晶圆制造论坛上公布了一个重磅消息,三星正在开发一个名为Gate All Around的技术,它将把三星的制程工艺推向3nm,并在2022年实现量产。

当然,长期关注芯片行业的同学都懂得,和“老冤家”台积电形成鲜明对比,三星的调性一向是“说得比做得漂亮”,在信守承诺这件事儿上,最好不要对其抱有太多期待,尤其是在7nm量产还看不到影子的现在。

三星喊出的预期进展,我们听听就好,但三星同时宣布的GAA技术却值得一波关注,在突破传统制程工艺5nm的限制后,“摩尔定律”的故事要怎样讲下去呢?

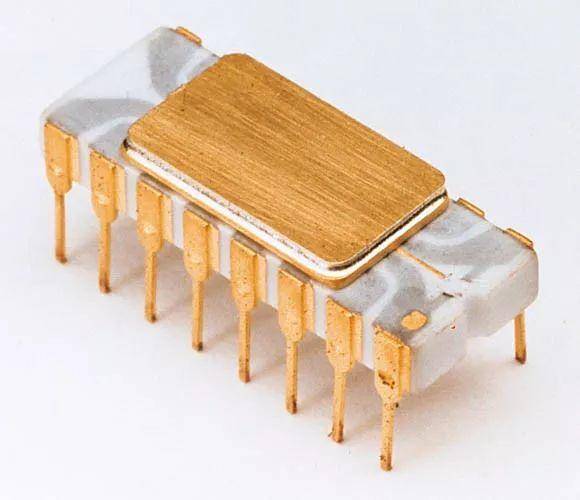

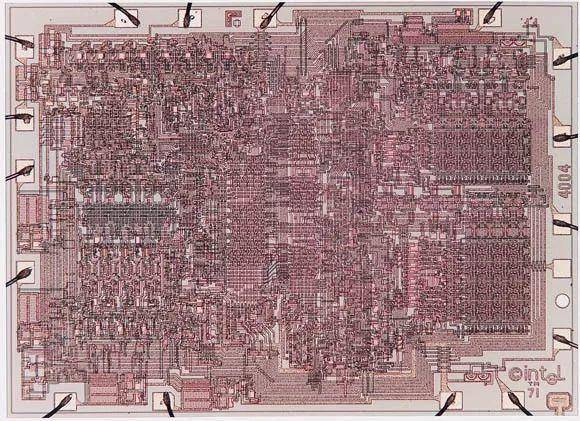

1971年11月15日,英特尔在美国《电子新闻报》上刊登了一则广告,广告的主角是一种新型芯片,它可以根据你的指令来执行不同的操作。

这枚芯片就是Intel 4004,人类历史上第一枚微型电脑处理器,它在3mm×4mm的尺寸里塞进了2300个晶体管,采用了五层设计,10微米制程,每秒运算9万次,代表了当时最先进的半导体器件制造水平。

也就是在这枚芯片诞生的6年前,戈登·摩尔提出以自己名字命名的「摩尔定律」,这位英特尔的联合创始人提出了一个大胆的设想:集成电路上可容纳的元器件的数量每隔18至24个月就会增加一倍,性能也将提升一倍。

工程师们很给力,在此后的40年多间,尽管包括英伟达CEO黄仁勋在内的大佬们,时不时就会发出“摩尔定律已死”的感叹,但这些言论总以更高制程芯片诞生的打脸定律而告终。

1992年,英特尔奔腾处理器采用了0.8微米的制程。

1996年,0.35微米制程芯片出现在任天堂游戏机上,成为了塞尔达传说、超级马里奥等景点游戏背后的底层技术基础。

2004年,包括IBM、英特尔、AMD、英飞凌在内的厂商先后推出了90nm芯片,制程工艺第一次从μm微米进化到了nm纳米。

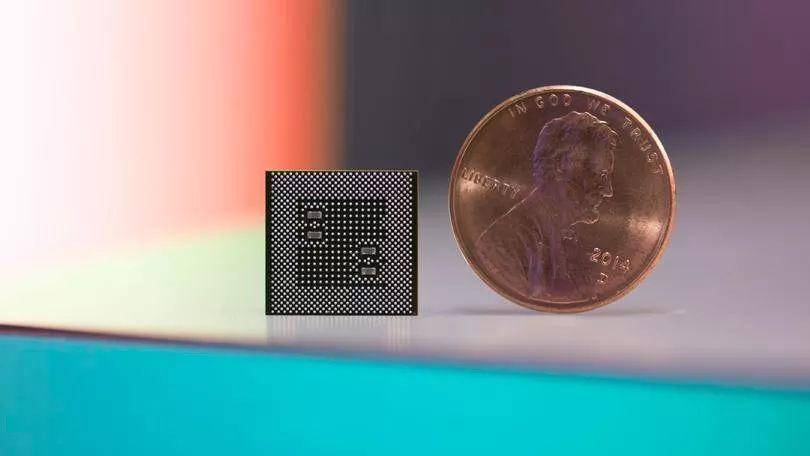

2010年,手机芯片取代笔记本电脑成为推动制程工艺继续发展的主要动力,这一年,诞生了三星Exynos 9和高通骁龙835等采用10nm制程的芯片。

2018年,苹果在iPhone XS上首先用上了7nm制程的A12 Bionic芯片;紧随其后,高通的骁龙855和华为海思的麒麟980也采用了台积电的7nm工艺,自此,人类的半导体器件制造工艺正式进入7nm时代。

如果你仔细观察半导体工艺制程的节点,会发现这些数字几乎都是以0.7倍的速度递减,按照这个传统的工艺路线来看,其后一代将是5nm制程芯片,这也将是现在使用的EUV光刻机能制造出的最高制程芯片。

然而,眼看就要从积累50年的“量变”迈向“质变”,包括台积电、三星在内的半导体制造大厂,已经纷纷将目光投向了代表“下一世代”的3nm制程,5nm这一步大家显然都已无心再关注,鼓捣7nm的空档顺手搞一搞就好。

从5nm到3nm到底有什么难的?

两个最大的障碍是光刻机技术的发展,和晶体管的结构。

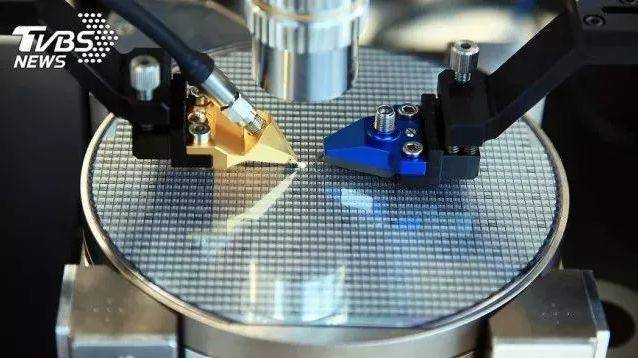

通俗地解释一下,光刻机的作用,类似于胶片相机,就是将已经设计好的电路图,通过激光投影“刻”到硅晶圆上。

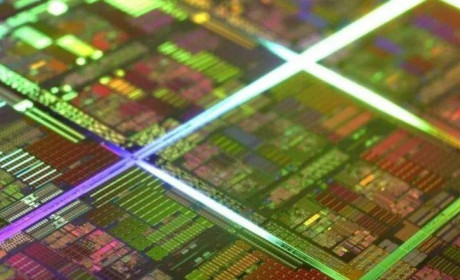

所谓的制程,就是指硅晶圆上微型电路之间的距离。当然这个数字越小,就意味着单位面积上可以容纳更多的元器件,随之提升的就是芯片的算力,与电信号的传播效率。使用低制程芯片的手机,直观上的感受起来更加轻薄、不卡顿、也更省电。

而在现有光刻机技术达到极限后,如何缩小晶体管的体积,就成为了决定芯片进步的最关键因素。

但由于受到很多复杂因素的影响(比如迁移率、漏电流等),晶体管的微型化并不是简单做小点就能解决的,相应地,它需要晶体管结构设计上的调整。

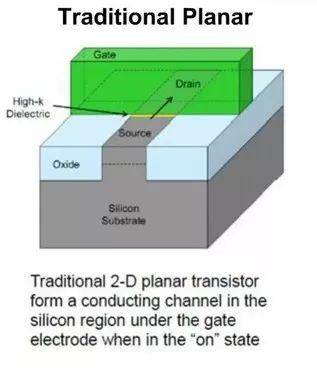

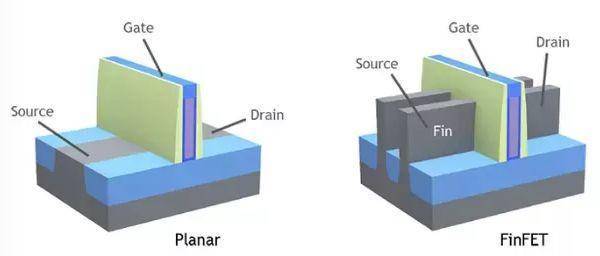

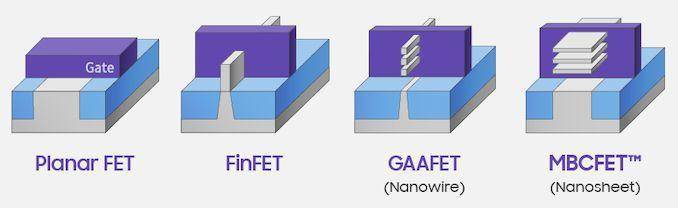

起初,晶体管是以平面的顺序排列,然而这种方式注定无法最大限度利用空间,当晶体管的尺寸缩小到25nm以下时,这种传统的平面场效应管(PlanarFET)的尺寸就已达到其物理极限。

随后,一种叫做FinFET的晶体管结构诞生了,在此前的很长一段时间内,它都是半导体界的主流解决方案,成为了驱动芯片产业发展的最大动力。

FinFET的主要思想就是将晶体管的排列立体化,通过在垂直方向的缩放来增加晶体管的沟到和栅极之间的接触面积,从而得到更快的切换时间与电流密度。

然而,和PlanarFET一样,FinFET也并非终极解决方案,当芯片制程来到3nm时,它就显得心有余而力不足了,芯片核心晶体管又面临着重新的设计和改造。

这个方案就是三星即将用到的GAA结构,即多闸极晶体管。不过,三星也在GAA的基础上做了改良,把晶体管通道从原来的小圆柱体,换成了更宽的纳米片,纳米片越宽,芯片的性能也越高,但随之而来的功耗也越大。

按照三星的设想,相较于7nm,采用3nm制程后,芯片性能将提高35%,功耗降低了50%,芯片面积缩小45%。

自从1971年第一枚10微米芯片诞生至今,几乎没有任何一个制程的芯片能具备3年以上的统治力。而从目前的情况来看,即便按照三星的理想进程计算,最早在2022年前,我们仍将停留在5nm的时代。

我们正在上一个世代中无限逼近摩尔定律的瓶颈,而当跨越这个节点后,我们对世界认知的极限是必定会随着拓宽。

人类用了30年的时间,将芯片制程从微米级带到纳米级;而从纳米向皮米(纳米的千分之一)的突破,又会是个怎么样的故事呢?

NEXTTECH

NEXTTECH